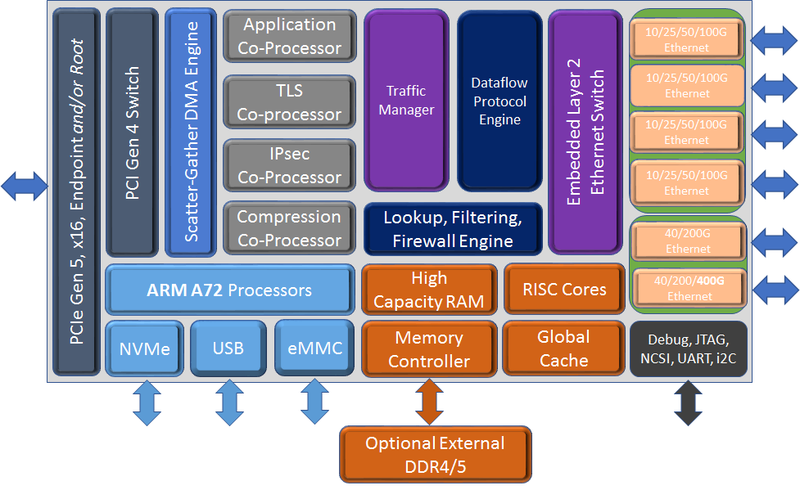

Chelsio Communications a annoncé la septième génération de ses processeurs réseau Terminator avec prise en charge 400GbE. Ce qui distingue le T7 de ses prédécesseurs est une partie informatique polyvalente plus avancée, qui comprend jusqu'à 8 cœurs Arm Cortex-A72, ils peuvent donc déjà être appelés DPU. Au total, cinq variantes de 5 puces sont présentées (T7, N7, D7, S74 et S72), qui diffèrent les unes des autres par un ensemble de moteurs et d'accélérateurs. La plate-forme T7 de référence sera disponible en mai, les premiers adaptateurs basés sur les nouveaux DPU devraient être attendus au troisième trimestre 2022.

Il existe des coprocesseurs distincts pour les tâches de compression, de déduplication ou de cryptographie. Le commutateur L2 intégré, familier à la série Unified Wire, n'est pas allé nulle part non plus. Le T7 utilise désormais le bus PCIe 5.0 x16 pour se connecter à l'hôte, et il contient également le complexe racine. De plus, il existe un commutateur intégré + un pont PCIe 4.0 et une interface NVMe, et même la prise en charge de l'émulation NVMe. Tout cela, par exemple, vous permet de créer facilement et rapidement un stockage NVMe-oF ou un pont NVMe-NVMe pour la compression à la volée et le chiffrement des données. La nouveauté offre une accélération de RoCEv2 et iWARP, FCoE et NVMe/TCP, iSCSI et iSER, ainsi que RAID5/6. La partie réseau prend en charge le déchargement Open vSwitch et Virt-IO.

Cependant, il n'y a pas de support P4 ici - Chelsio continue d'utiliser ses propres moteurs pour traiter le trafic. Mais les développements réalisés pour les séries T5 et T6 seront plus facilement transposables sur une nouvelle génération de puces. De plus, la télémétrie "profonde" de tout le trafic transitant par le DPU, qui est désormais pratiquement obligatoire, est apparue pour augmenter la gérabilité et le protéger. Si cela ne suffit pas, vous pouvez connecter directement un FPGA au T7 (et au D7) et étendre la mémoire embarquée avec des banques DDR4 / 5. Le communiqué de presse note également que le T7 peut être un digne remplaçant d'InfiniBand dans les systèmes HPC.

L'option D7 est la plus proche du T7, mais n'offre qu'une connexion 200GbE, manque de certaines fonctions et interfaces secondaires, et est généralement conçue pour créer un système de stockage. N7, en revanche, manque de cœurs Arm et de toutes les fonctions pour travailler avec des stockages, il n'a pas de commutateur PCIe et de pont. Il ne propose que des interfaces 200GbE. Enfin, les puces de la série S7 manquent d'un certain nombre de fonctionnalités secondaires et ne fournissent qu'une connectivité 100/200GbE. Ils sont plus susceptibles d'être des SmartNIC, car ils sont complètement dépourvus de cœurs Arm et de certaines fonctions. Mais ils sont également peu coûteux.

De plus, dans la septième génération de Termintator, il est devenu possible de se passer de DRAM embarquée tout en conservant toutes les fonctionnalités. Ainsi, l'utilisation de la mémoire hôte réduira davantage le coût des solutions finales qui seront créées par les équipementiers. Les puces elles-mêmes sont fabriquées à l'aide de la technologie de processus TSMC 12 nm FFC, de sorte que même l'ancienne version des puces a une consommation électrique typique inférieure à 22 W.

2022-04-29 05:30:20

Auteur: Vitalii Babkin