Le concepteur de puces semi-conductrices Alphawave a annoncé avoir produit le premier prototype de puce de l'industrie en utilisant le processus N3E 3 nm amélioré de TSMC. Il est à noter que l'échantillon de test a passé avec succès tous les tests nécessaires.

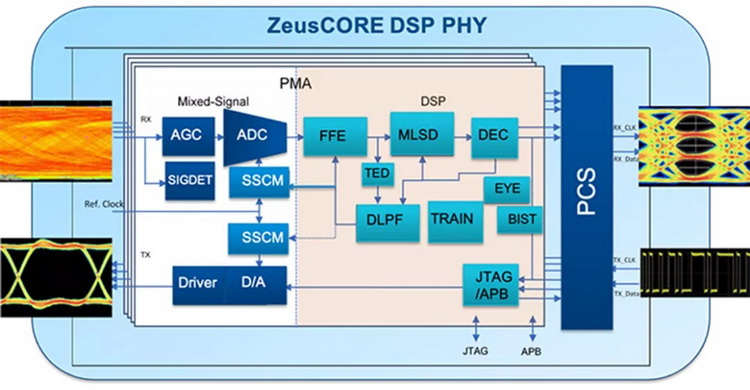

Pour Alphawave, un échantillon de puce ZeusCORE100 1-112 Gbps NRZ/PAM4 Serialiser-Deserialiser (SerDes) a été lancé. Il s'agit d'une paire de blocs fonctionnels couramment utilisés dans les communications à haut débit pour convertir les données entre les interfaces série et parallèle dans les deux sens. Il est à noter qu'il prend en charge diverses nouvelles normes d'interface, notamment 800G Ethernet, OIF 112G-CEI, PCIe 6.0 et CXL3.0. Ces puces sont principalement utilisées pour les communications dans les systèmes de serveurs.

TSMC prévoit d'introduire cinq variantes du processus 3 nm d'ici deux à trois ans. La version régulière du processus N3 sera utilisée par les principaux clients d'un fabricant de puces sous contrat, tel qu'Apple. Avec l'introduction de la deuxième génération de la technologie de procédé 3 nm (N3E), il est prévu d'accélérer et d'augmenter la production de microcircuits, d'améliorer leurs performances et leur efficacité énergétique.

Les puces basées sur le processus N3E avancé de 3 nm devraient être plus largement utilisées que les puces basées sur le processus N3 standard, cependant, le début de la production en série de puces basées sur le processus N3E n'est pas prévu avant la mi-2023, c'est-à-dire environ un an après le début de la production en série de puces basées sur le procédé N3E.production de puces selon N3.

Après le passage à la production de masse de puces selon les normes N3E, TSMC prévoit de passer à la production de puces basées sur les processus de fabrication N3P et N3S, qui seront des options pour optimiser N3E pour différentes classes d'applications. N3P se concentre sur les puces hautes performances, tandis que N3S se concentre sur les puces économes en énergie avec une densité de transistors accrue. Les deux processus techniques sont prévus pour 2024. D'ici 2025, lorsque l'entreprise commencera à maîtriser la prochaine étape des normes relatives aux semi-conducteurs, une autre technologie de traitement de classe 3 nm apparaîtra - N3X. Sur sa base, des processeurs hautes performances seront produits, pour lesquels l'utilisation de courants de fonctionnement élevés et un fonctionnement à long terme à des fréquences d'horloge accrues sont importants.

2022-10-26 14:21:19

Auteur: Vitalii Babkin