RISC-V アーキテクチャは非常に新しく、通常は Raspberry Pi のようなボード上の費用対効果の高いチップに関連付けられています。 ただし、技術的には、Arm および x86 アーキテクチャに基づく最高のソリューションと競合できる強力なプロセッサを作成することもできます。 RISC-V サミットで、Ventana Micro Systems は高性能プロセッサのファミリ全体を発表しました。その最初のものは Veyron V1 チップでした。ハイエンドCPU。

目新しさはハイパースケーラー市場を対象としており、チップレット設計のおかげで、新しいプロセッサはもともと顧客のタスクに合わせてカスタマイズできるように開発されました。 Veyron V1は、1つ以上のVeyronコンピューティングチップレット、I / Oハブ、およびすべてのコンポーネントを一緒に接続できる相互接続を含む一種のキットコンストラクターの形で提供されます. 開発者によると、これにより、新しいプロセッサプラットフォームの導入コストが大幅にスピードアップして削減され、チップの開発コストが 75% 削減され、作成時間が 2 年以内に短縮されるはずです。

Veyron V1 コンピューティング チップレットは、高度な 64 ビット RISC-V コアを使用し、2 MB の L2 キャッシュとマルチスレッド メモリ コントローラーを備えています。 チップレット構成は、約 3 GHz で 6、8、12、または 16 コアで利用できます。これは、Google および AWS ソリューションに匹敵します。 このプロセッサは、データセンターだけでなく、さまざまな組み込みシステム、5G 基地局、さらにはクライアント ワークステーションでも使用できます。

Veyron V1 のアーキテクチャ設計では、8 段階の順不同で積極的なパイプラインを使用しています。 このチップは、TSMC の 5nm プロセス技術を使用して、最大 3.6GHz で動作することができます。 I/O ハブは、安価な 12nm または 16nm プロセスを使用して作成できます。 プロセッサ コンポーネントを接続するために、特別な低レイテンシ D2D インターコネクトが開発されました。

各チップレットには最大 16 個のコアが含まれており、プロセッサは 12 個のチップレットで最大 192 個のコアまで拡張できます。 共有 L3 キャッシュの合計は 48 MB です。 サードパーティのチャネルを介した攻撃に対するアーキテクチャの高レベルの保護が宣言されています。 開発者は、前例のない低消費電力を主張しています。128 個の V1 コアが 280 W に収まります。 AMD EPYC 7763 は半分のコア数で同じ量を消費します。

Ventana の発表は「紙」とは言えません。さらに、デスクトップと 2U サーバー シャーシの 2 種類のシャーシで同時に開発者キットが利用できることについて同社は述べています。 構成には、CXL (PCIe 5.0) x16 インターフェイス経由で接続された 16 コア V1、128GB DDR5、2 つの空き PCIe 5.0 x16 拡張スロット、NVMe M.2 ブート ドライブ、リモート管理用の 8 つの NVMe SFF 2.5" SSD 1GbE ポートが含まれます。

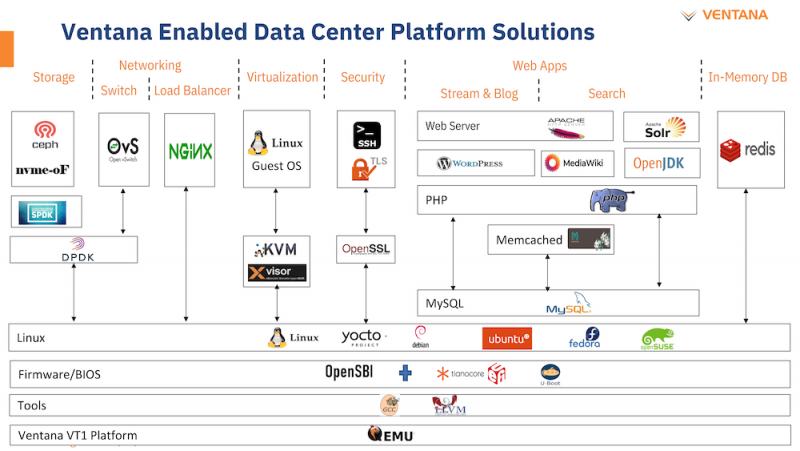

同社はソフトウェア サポートも忘れていません。Ventana Veyron V1 開発者プラットフォームには、主要なソフトウェアが既に新しいアーキテクチャに移植された本格的な SDK が付属しています。 このリストには、GCC および LLVM コンパイラ、OpenOCD/GDB デバッガー、U-Boot および Tianocore UEFI EDK2.1 ローダーのソースとバイナリが含まれています。 多くの Linux ディストリビューションがサポートされており、その他のシステムおよびアプリケーション ソフトウェアもサポートされています。 新しいシステムは、来年初めに利用可能になる予定です。

2022-12-14 08:08:37

著者: Vitalii Babkin

ソース URL