Die Arm Cortex-M-Familie umfasst relativ kostengünstige Lösungen, die auf minimalen Stromverbrauch ausgerichtet sind. SoCs, die auf solchen Kernen basieren, liegen normalerweise verschiedenen eingebetteten Systemen und Geräten der IoT-Klasse zugrunde. Entwicklungen aus der Welt der „großen“ Cortex-A dringen jedoch in dieses Segment ein: Bereits im Februar 2020 kündigte das Unternehmen die Cortex-M55 (ARMv8.1-M)-Serie an, doch jetzt weicht sie einem neuen Marktführer – Cortex -M85.

Für seine Klasse ist dies in vielerlei Hinsicht ein einzigartiger Prozessorkern. Beim Integer-Computing ist er dem Cortex-M7 mit seiner sechsstufigen superskalaren Pipeline voraus, und beim Arbeiten mit Helium-Vektorerweiterungen, die im Cortex-M55 debütierten, ist er schneller als letzterer. Die Neuheit ist für Geräte gedacht, die eine ausreichend hohe Performance, aber gleichzeitig Eigenschaften wie deterministisches Verhalten und geringe Latenz bei der Interrupt-Verarbeitung benötigen.

Der neue Kern basiert auf dem gleichen Befehlssatz, ARMv8.1-M, hat aber eine siebenstufige Integer-Block-Pipeline, optionale FPUs mit FP16/32/64-Unterstützung und Helium-Vektorerweiterungen (M-Profil). Eine zusätzliche 64-Bit-Schnittstelle ermöglicht es dem Kernel, mit benutzerdefinierten Beschleunigern (bis zu 8) und Anweisungen zu arbeiten. 32-Bit-DSP/SIMD-Erweiterungen sind verfügbar. Daten- und Befehls-Caches der ersten Ebene sind jeweils bis zu 64 KB groß, und Caches höherer Ebene können bis zu 16 MB groß sein.

Das MPU-Speicherschutzmodul wird optional unterstützt – bis zu 16 isolierte Regionen mit unterschiedlichen Sicherheitsstufen bei vorhandener TrustZone. Der integrierte NVIC (Nested Vectored Interrupt Controller) Interrupt Controller unterstützt bis zu 480 Interrupts sowie NMI. Separat ist ein Weck-Controller implementiert, um den Prozessor schnell aus den Schlafmodi zu verlassen.

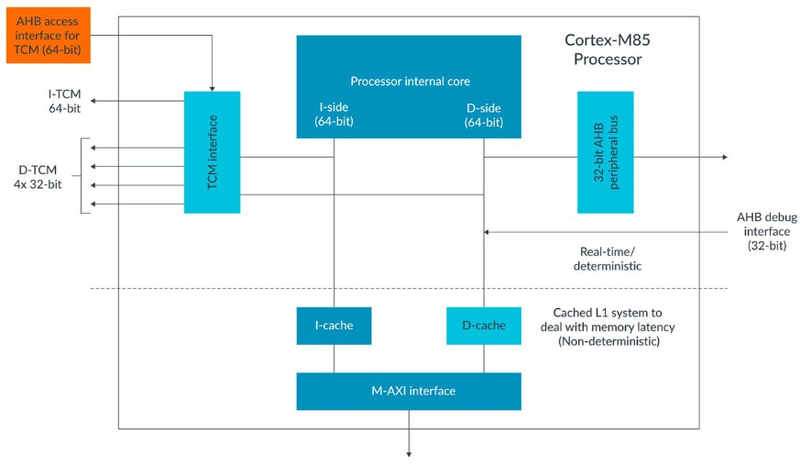

Der Cortex-M85 bietet erweiterte Debugging-Tools, einschließlich eines Leistungsmonitors und optionaler Trace-Blöcke. Arm TrustZone und Erweiterungen (Pointer Authentication, Branch Target Identification) sind für die Sicherheit verantwortlich, sodass der neue Kern die Anforderungen von PSA Certified Level 2 erfüllt. Der Kern kommuniziert mit der Außenwelt über drei Busse – den wichtigsten 64-Bit-AMBA 5 AXI , kompatibel mit der AXI4-Version und zwei Reifen AMBA 5 AHB, von denen einer für Peripheriegeräte verwendet wird.

Er ist derzeit der schnellste Arm-Kern der M-Familie – seine Leistung wird auf 6,28 CoreMark/MHz und 8,76DMIPS/MHz geschätzt. Es ist als Teil der Referenzplattformen Corstone-310 und Ethos-U55 erhältlich. Lösungen auf Basis neuer Produkte können jetzt mit Hilfe von Arm Virtual Hardware entwickelt werden, denn fertige Chips mit neuen Kernen dürften frühestens in einem Jahr erscheinen. Weitere Details zum neuen Produkt finden Sie in der Ankündigung und im Entwicklerbereich der Arm-Website.

2022-04-27 20:55:10

Autor: Vitalii Babkin