La famiglia Arm Cortex-M comprende soluzioni relativamente economiche focalizzate sul consumo energetico minimo. SoC basati su tali core di solito sono alla base di vari sistemi embedded e dispositivi di classe IoT. Tuttavia, gli sviluppi dal mondo del Cortex-A "grande" penetrano in questo segmento: già a febbraio 2020, l'azienda ha annunciato la serie Cortex-M55 (ARMv8.1-M), ma ora sta cedendo il passo a un nuovo leader: Cortex -M85.

Per la sua classe, questo è davvero un core del processore unico sotto molti aspetti. Nell'integer computing, è in vantaggio rispetto al Cortex-M7 con la sua pipeline superscalare a sei stadi e quando si lavora con le estensioni vettoriali dell'elio, che ha debuttato nel Cortex-M55, è più veloce di quest'ultimo. La novità è destinata a dispositivi che richiedono un livello di prestazioni sufficientemente elevato, ma allo stesso tempo caratteristiche come comportamento deterministico e bassa latenza durante l'elaborazione degli interrupt.

Il nuovo core è costruito sullo stesso set di istruzioni, ARMv8.1-M, ma ha una pipeline di blocchi interi a sette stadi, FPU opzionali con supporto FP16/32/64 ed estensioni vettoriali Helium (profilo M). Un'interfaccia aggiuntiva a 64 bit consente al kernel di lavorare con acceleratori personalizzati (fino a 8) e istruzioni. Sono disponibili estensioni DSP/SIMD a 32 bit. Le cache di dati e istruzioni di primo livello sono fino a 64 KB ciascuna e le cache di livello superiore possono arrivare a 16 MB.

Il modulo di protezione della memoria MPU è supportato opzionalmente: fino a 16 regioni isolate con diversi livelli di sicurezza in presenza di TrustZone. Il controller di interrupt integrato NVIC (Nested Vectored Interrupt Controller) supporta fino a 480 interrupt e NMI. Separatamente, viene implementato un controller di riattivazione per uscire rapidamente dal processore dalle modalità di sospensione.

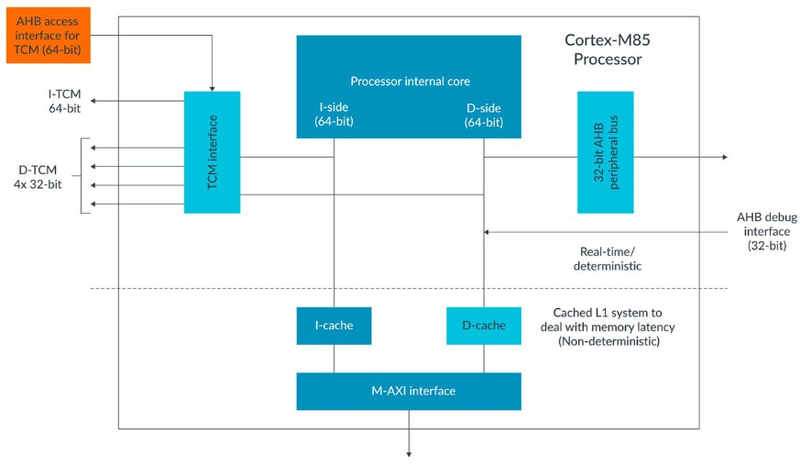

Cortex-M85 fornisce strumenti di debug avanzati, tra cui un monitor delle prestazioni e blocchi di traccia opzionali. Arm TrustZone e le estensioni (Pointer Authentication, Branch Target Identification) sono responsabili della sicurezza, in modo che il nuovo core soddisfi i requisiti del PSA Certified Level 2. Il core comunica con il mondo esterno attraverso tre bus: il principale AMBA 5 AXI a 64 bit , compatibile con la versione AXI4 e due pneumatici AMBA 5 AHB, di cui uno utilizzato per le periferiche.

Attualmente è il core Arm più veloce della famiglia M: le sue prestazioni sono stimate a 6,28 CoreMark / MHz e 8,76DMIPS / MHz. È disponibile come parte delle piattaforme di riferimento Corstone-310 ed Ethos-U55. Soluzioni basate su nuovi prodotti possono essere sviluppate ora con l'aiuto di Arm Virtual Hardware, poiché è probabile che i chip già pronti con nuovi core compaiano non prima di un anno. Maggiori dettagli sul nuovo prodotto possono essere trovati nell'annuncio e nella sezione sviluppatori del sito web di Arm.

2022-04-27 20:55:10

Autore: Vitalii Babkin