Le PDG d'Intel, Patrick Gelsinger, a pris la parole lors de la conférence annuelle Hot Chips, qui se déroule virtuellement cette année. Au cours de son discours, il a parlé de l'ère à venir de la fabrication de puces à transistors à un billion de milliards. Intel croit toujours que l'avenir réside dans ses technologies et ses processeurs multi-puces.

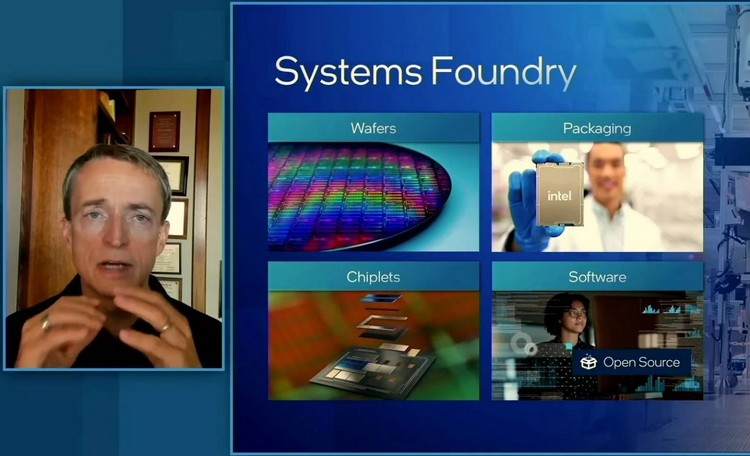

Gelsinger affirme que cette décision marque une transition d'une ère de fabrication de tranches uniques à ce qu'il appelle une ère de fabrication de systèmes, qui sera alimentée par une combinaison d'avancées dans la fabrication de tranches de silicium, le conditionnement des puces et les logiciels.

La force motrice est désormais que les clients ne veulent pas seulement plus de puces, ils ont besoin de puces plus puissantes à mesure que les modèles d'IA deviennent plus complexes et que les volumes de données augmentent. Intel s'attend à franchir le cap du billion de transistors dans une seule puce (qui sera composée de plusieurs matrices) d'ici 2030.

"Aujourd'hui, il y a environ 100 milliards de transistors dans un processeur, et nous voyons que nous pouvons atteindre un billion d'ici la fin de la décennie", a déclaré Gelsinger. "Avec RibbonFET, nous avons une nouvelle structure de transistor révolutionnaire que nous sommes sur le point de construire et qui, selon nous, continuera à évoluer pendant le reste de la décennie." RibbonFET est une nouvelle version de l'architecture de transistor Gate-All-Around (GAA) dans laquelle le matériau de grille est fermé dans un anneau autour d'un canal conducteur.

La façon de créer des systèmes plus grands et plus puissants est de les construire à partir de pièces plus petites, dit Gelsinger, permettant des "capacités hétérogènes personnalisées", et c'est là que les technologies de conditionnement 2D et 3D entrent en jeu, donnant aux fabricants de puces les outils pour "appliquer le bon transistor". "pour résoudre le problème."

Dans ce cas, ce que Gelsinger veut dire, c'est que les puces individuelles peuvent être fabriquées à l'aide de n'importe quelle technologie de processus qui convient le mieux à leur puissance, leurs capacités RF, leur logique et leur mémoire, puis assemblées à l'aide de technologies de conditionnement avancées pour former une puce complète.

La clé sera de normaliser la façon dont toutes ces parties se connectent les unes aux autres, comme l'a mentionné Gelsinger en parlant des efforts d'Intel pour développer Universal Chiplet Interconnect Express (UCIe) en tant que norme de l'industrie pour l'interconnexion des puces basées sur la norme PCIe. Selon Gelsinger, UCIe permettra de construire des puces en utilisant différentes puces de différents fabricants.

"Vous pouvez avoir deux puces d'Intel, une de l'usine TSMC, un contrôleur d'alimentation de Texas Instruments, un contrôleur d'E/S de Global Foundries, et bien sûr, comme Intel dispose de la meilleure technologie de conditionnement, il peut assembler toutes ces puces. , bien qu'il puisse s'agir d'un assembleur différent, donc comme nous pouvons le voir, il y a un mix and match », a déclaré Gelsinger.

Aucun discours d'Intel n'est complet sans une mention de la loi de Moore, et cette fois Gelsinger a également déclaré que toutes ces avancées sont basées sur la poursuite de ce postulat : "La loi de Moore, le doublement constant des capacités des transistors à mesure qu'ils rétrécissent avec le temps, est un facteur fondamental tout ce que nous avons pu réaliser <..> Intel continuera à faire progresser la loi de Moore.

2022-08-23 22:22:58

Auteur: Vitalii Babkin