Intel CEO の Patrick Gelsinger は、今年バーチャルで開催される毎年恒例の Hot Chips カンファレンスで講演しました。講演の中で、彼は来るべき兆トランジスタ チップ製造の時代について語った。 Intel は、将来は自社の技術とマルチチップ プロセッサにかかっていると今でも信じています。

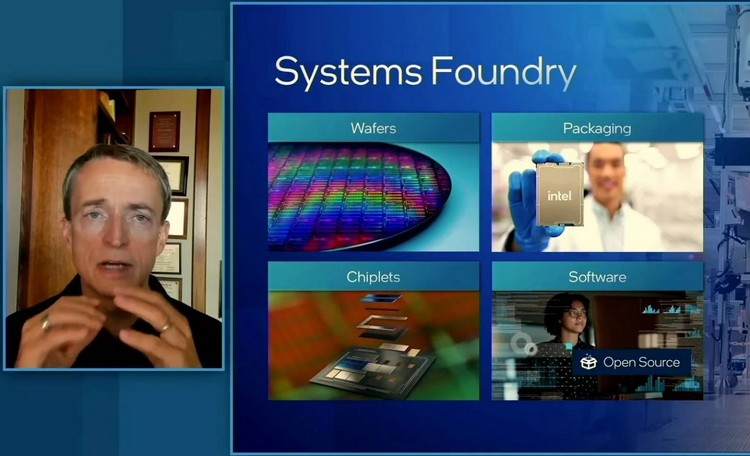

Gelsinger 氏は、この動きは、単一ウエハー製造の時代から、シリコンウエハー製造、チップパッケージング、およびソフトウェアの進歩の組み合わせによって強化されるシステム製造の時代への移行を示していると述べています。

AIモデルがより複雑になり、データ量が増加するにつれて、顧客はより多くのチップを必要とするだけでなく、より強力なチップを必要としていることが現在の原動力となっています. Intel は、2030 年までに単一のチップ (複数のダイで構成される) で 1 兆個のトランジスタのマイルストーンを達成すると予想しています。

「現在、プロセッサ パッケージには約 1,000 億個のトランジスタが含まれており、10 年の終わりまでに 1 兆個に達する可能性がある」と Gelsinger 氏は述べています。 「RibbonFET により、画期的な新しいトランジスタ構造が構築されようとしていますが、これは今後 10 年間にわたって拡大し続けると考えています。」リボンFETはゲートオールアラウンド(GAA)トランジスタアーキテクチャの新しいバージョンであり、ゲート材料が導電チャネルの周りのリングで閉じられています。

より大きくより強力なシステムを作成する方法は、より小さな部品からそれらを構築することであり、「カスタム異種機能」を可能にすることであり、2D および 3D パッケージング技術の出番であり、チップメーカーに「適切なトランジスタを適用するためのツールを提供します。 「問題を解決するために。」

この場合、Gelsinger が意味することは、個々のチップは、電力、RF 機能、ロジック、およびメモリに最適なプロセス技術を使用して製造され、高度なパッケージ技術を使用して組み立てられ、完全なチップを形成できるということです。

PCIe 標準に基づいてチップを相互接続するための業界標準として Universal Chiplet Interconnect Express (UCIe) を開発する Intel の取り組みについて話しているときに Gelsinger が述べたように、重要なのは、これらすべての部品が相互に接続する方法を標準化することです。 Gelsinger 氏によると、UCIe により、さまざまなメーカーのさまざまなチップを使用してチップを構築できるようになります。

「Intel の 2 つのチップ、TSMC 工場の 1 つ、Texas Instruments の電源コントローラー、Global Foundries の I/O コントローラーを使用できます。もちろん、Intel は最高のパッケージング技術を持っているため、これらすべてのチップを組み合わせることができます。 、それは別のアセンブラーである可能性がありますが、ご覧のとおり、さまざまな組み合わせがあります」と Gelsinger 氏は述べています。

ムーアの法則に言及せずに Intel の話は完結しません。今回、ゲルシンガーは、これらすべての進歩は次の仮説の継続に基づいているとも述べました。これまで達成してきたすべての基本的な要因 <..> インテルは、ムーアの法則を前進させ続けます。

2022-08-23 22:22:58

著者: Vitalii Babkin