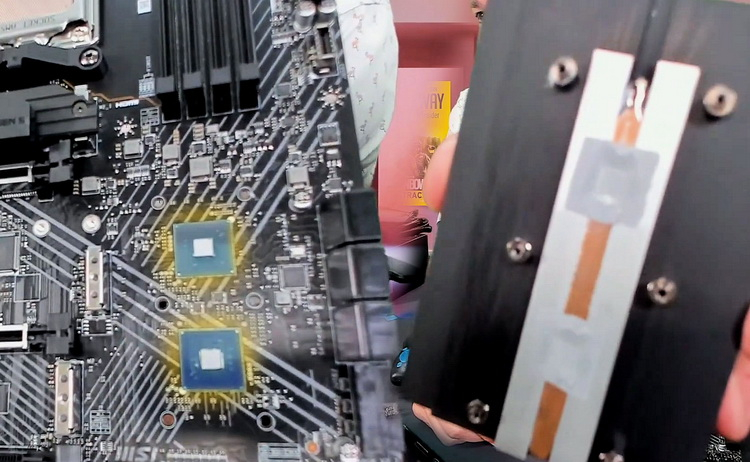

MSI a montré le chipset AMD X670 en direct sur l'une de ses cartes mères sans dissipateur thermique installé dans le cadre de son MSI Insider Livestream. Il se compose en fait de deux microcircuits. Plus tôt, AMD lui-même a confirmé que les anciens chipsets sont un ensemble de deux puces AMD B650, mais la société ne les a pas montrés en direct.

MSI a précédemment confirmé que les systèmes Ryzen 7000 recevront la technologie AMD EXPO pour l'overclocking de la RAM DDR5, et a également publié un didacticiel vidéo sur l'installation de Ryzen 7000 dans le nouveau socket Socket AM5. AMD lui-même ne semble pas apprécier que son partenaire soit si direct dans la divulgation de ces informations. Évidemment, au Computex 2022, AMD voulait seulement partager de nouveaux détails sur ses processeurs de bureau de nouvelle génération, ainsi que sur la plate-forme sur laquelle ils seront utilisés. Il n'était pas question d'une annonce à part entière, du moins maintenant. Il est attendu cet automne.

Sous la pression d'AMD, MSI a tout de même dû supprimer certaines informations précédemment publiées. Cependant, le fabricant n'a pas renoncé à de nouvelles fuites, et la dernière a eu lieu en direct, où MSI a montré divers produits en préparation pour la sortie.

La nouvelle plate-forme AMD utilise le socket AM5 (LGA 1718) et prendra en charge les puces avec une consommation électrique maximale de 170 W. La première génération de processeurs pour Socket AM5 sera basée sur l'architecture Zen 4 et prendra en charge la mémoire DDR5 et l'interface PCIe 5.0. Les cartes mères des nouveaux processeurs seront équipées des chipsets AMD X670E, X670 et B650. Le premier et le second sont des ensembles logiques constitués de deux microcircuits B650. Ils prendront en charge jusqu'à 24 voies PCIe 5.0 pour le sous-système graphique et mémoire.

Le boîtier thermique d'un microcircuit des chipsets X670E et X670 est de 7 W, et les cartes basées sur X670 avec deux microcircuits éloignés l'un de l'autre sont tout à fait capables d'utiliser un refroidissement passif, ce qui serait difficile à réaliser si toutes les capacités de ces chipsets ont été implémentés dans une seule puce.

2022-05-26 11:13:44

Auteur: Vitalii Babkin